Performance Specification

# KAF- 6303E

# 3072 (H) x 2048 (V) Pixel

**Enhanced Response Full-Frame CCD Image Sensor**

**Performance Specification**

Eastman Kodak Company

**Image Sensor Solutions**

Rochester, New York 14650-2010

**Revision 3.1**

March 19, 2004

Eastman Kodak Company - Image Sensor Solutions

## **TABLE OF CONTENTS**

| 1.1 Features                                              | 3  |

|-----------------------------------------------------------|----|

| 1.2 Description                                           |    |

| 1.3 Image Acquisition                                     |    |

| 1.4 Charge Transport                                      | 4  |

| 1.5 Output Structure                                      | 4  |

| 1.6 Dark Reference Pixels                                 |    |

| 1.7 Dummy Pixels.                                         |    |

| 2.1 Package Drawing                                       |    |

| 2.2 Pin Description                                       |    |

| 3.1 Absolute Maximum Ratings                              | 7  |

| 3.2 DC Operating Conditions                               | 8  |

| 3.3 AC Operating Conditions                               | 9  |

| 3.4 AC Timing Conditions                                  | 9  |

| 4.1 Performance Specifications                            | 11 |

| 4.2 Typical Performance Characteristics Spectral Response | 12 |

| 4.3 Defect Classification                                 | 13 |

| 5.1 Quality Assurance and Reliability                     | 14 |

| 5.2 Ordering Information                                  | 15 |

| vision Changes16 |

|------------------|

|------------------|

#### FIGURES

| Figure 1 | Functional Block Diagram                  | _3  |

|----------|-------------------------------------------|-----|

|          | Package Diagram                           |     |

|          |                                           | 6   |

|          | Recommended Output Structure Load Diagram | . 8 |

|          |                                           | 10  |

|          |                                           |     |

Eastman Kodak Company - Image Sensor Solutions

#### 1.1 Features

- 6M Pixel Area CCD

- 3072H x 2048V (9 µm) Pixels

- Transparent Gate True Two Phase Technology (Enhanced Spectral Response)

- 27.65mm H x 18.48mm V Photosensitive Area

- 2-Phase Register Clocking

- 100% Fill Factor

- Low Dark Current ( <10pA/cm<sup>2</sup> @ 25<sup>o</sup>C)

#### 1.2 Description

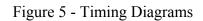

The KAF-6303E is a high performance monochrome area CCD (charge-coupled device) image sensor with 3072H x 2048V photo active pixels designed for a wide range of image sensing applications in the 0.3 nm to 1.0 nm wavelength band. Typical applications include military, scientific, and industrial imaging. A 74dB dynamic range is possible operating at room temperature.

The sensor is built with a true two-phase CCD technology. This technology simplifies the support circuits that drive the sensor and reduces the dark

current without compromising charge capacity. The transparent gate results in spectral response increased ten times at 400nm, compared to a front side illuminated standard polysilicon gate technology. The sensitivity is increased 50% over the rest of the visible wavelengths.

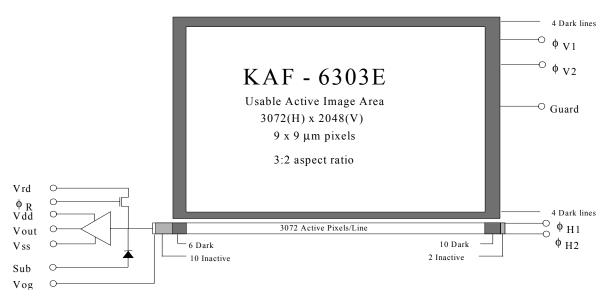

Total chip size is 29.0 mm x 19.1 mm and is housed in a 26-pin, 0.88" wide DIL ceramic package with 0.1" pin spacing.

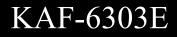

The sensor consists of 3088 parallel (vertical) CCD shift registers each 2056 elements long. These registers act as both the photosensitive elements and as the transport circuits that allow the image to be sequentially read out of the sensor. The elements of these registers are arranged into a 3072 x 2048 photosensitive array surrounded by a light shielded dark reference of 16 columns and 8 rows. The parallel (vertical) CCD registers transfer the image one line at a time into a single 3100 element (horizontal) CCD shift register. The horizontal register transfers the charge to a single output amplifier. The output amplifier is a two-stage source follower that converts the photo-generated charge to a voltage for each pixel

#### Figure 1 - Functional Block Diagram

Eastman Kodak Company - Image Sensor Solutions

#### **1.3** Image Acquisition

An electronic representation of an image is formed when incident photons falling on the sensor plane create electron-hole pairs within the sensor. These photoninduced electrons are collected locally by the formation of potential wells at each photogate or pixel site. The number of electrons collected is linearly dependent on light level and exposure time and non-linearly dependent on wavelength. When the pixel's capacity is reached, excess electrons will leak into the adjacent pixels within the same column. This is termed blooming. During the integration period, the  $\phi$ V1 and  $\phi$ V2 register clocks are held at a constant (low) level.

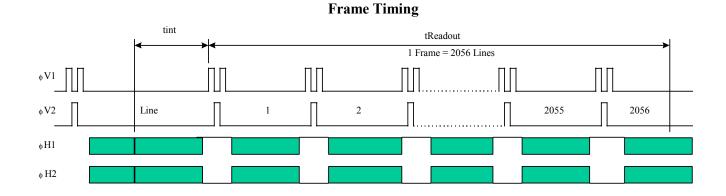

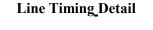

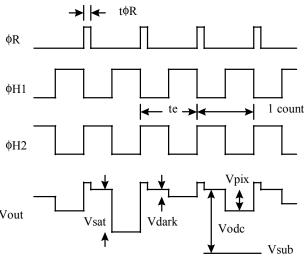

See Figure 5. - Timing Diagrams.

#### **1.4 Charge Transport**

Referring again to Figure 5 - Timing Diagrams, the integrated charge from each photogate is transported to the output using a two step process. Each line (row) of charge is first transported from the vertical CCD's to the horizontal CCD register using the  $\Phi$ V1 and  $\Phi$ V2 register clocks. The horizontal CCD is presented a new line on the falling edge of  $\Phi$ V2 while  $\Phi$ H1 is held high. The horizontal CCD's then transport each line, pixel by pixel, to the output structure by alternately clocking the  $\Phi$ H1 and  $\Phi$ H2 pins in a complementary fashion. On each falling edge of  $\Phi$ H2 a new charge packet is transferred onto a floating diffusion and sensed by the output amplifier

#### 1.5 Output Structure

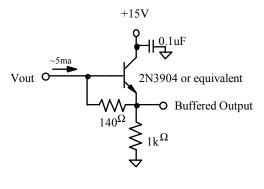

Charge presented to the floating diffusion (FD) is converted into a voltage and current amplified in order to drive off-chip loads. The resulting voltage change seen at the output is linearly related to the amount of charge placed on FD. Once the signal has been sampled by the system electronics, the reset gate ( $\phi$ R) is clocked to remove the signal and FD is reset to the potential applied by Vrd. More signal at the floating diffusion reduces the voltage seen at the output pin. In order to activate the output structure, an off-chip load must be added to the Vout pin of the device - see Figure 4.

#### **1.6 Dark Reference Pixels**

Surrounding the peripheral of the device is a border of light shielded pixels. This includes 6 leading and 10 trailing pixels on every line excluding dummy pixels. There are also 4 full dark lines at the start of every frame and 4 full dark lines at the end of each frame. Under normal circumstances, these pixels do not respond to light. However, dark reference pixels in close proximity to an active pixel, or the outer bounds of the chip (including the first two lines out), can scavenge signal depending on light intensity and wavelength and therefore will not represent the true dark signal.

#### 1.7 Dummy Pixels

Within the horizontal shift register are 10 leading and 2 trailing additional shift phases that are not associated with a column of pixels from the vertical register. These pixels contain only horizontal shift register dark current signal and do not respond to light. A few leading dummy pixels may scavenge false signal depending on operating conditions.

Eastman Kodak Company - Image Sensor Solutions

KAF-6303E

#### 2.1 Package Drawing

Figure 2 - Package Drawing

Eastman Kodak Company - Image Sensor Solutions

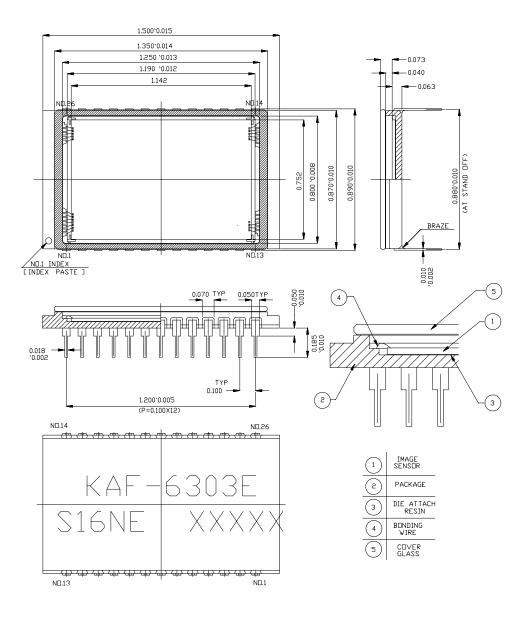

### 2.2 Pin Description

| Pin                  | Symbol | Description              | Pin               | Symbol          | Description                    |

|----------------------|--------|--------------------------|-------------------|-----------------|--------------------------------|

| 1, 13, 14,<br>15, 26 | Vsub   | Substrate (Ground)       | 10                | ¢ <sub>H1</sub> | Horizontal CCD Clock - Phase 1 |

| 2                    | Vout   | Video Output             | 11                | <b>Ф</b> Н2     | Horizontal CCD Clock - Phase 2 |

| 3                    | Vdd    | Amplifier Supply         | 16, 17,<br>22, 23 | ФV1             | Vertical CCD Clock - Phase 1   |

| 4                    | Vrd    | Reset Drain              | 18, 19,<br>20, 21 | ф <sub>V2</sub> | Vertical CCD Clock - Phase 2   |

| 5                    | φR     | Reset Clock              | 24                | Vguard          | Guard Ring                     |

| 6                    | Vss    | Amplifier Supply Return  | 25                | Vog             | Output Gate                    |

| 7, 8, 9, 12          | N/C    | No connection (open pin) |                   |                 |                                |

Figure 3 - Package Pin Designations

Eastman Kodak Company - Image Sensor Solutions

#### 3.1 Absolute Maximum Ratings

| Description                | Symbol           | Min. | Max. | Units | Notes |

|----------------------------|------------------|------|------|-------|-------|

| Diode Pin Voltages         | Vdiode           | 0    | 20   | V     | 1.2   |

| Gate Pin Voltages - Type 1 | Valode<br>Vgate1 | -16  | 16   | V     | 1, 2  |

| Gate Pin Voltages - Type 2 | Vgate2           | 0    | 16   | V     | 1,4   |

| Inter-Gate Voltages        | Vg-g             |      | 16   | V     | 5     |

| Output Bias Current        | Iout             |      | -10  | mA    | 6     |

| Output Load Capacitance    | Cload            |      | 15   | pF    | 6     |

| Storage Temperature        | Т                | 0    | 70   | °C    |       |

| Humidity                   | RH               | 5    | 90   | %     | 7     |

Notes:

- 1. Referenced to pin Vsub.

- 2. Includes pins: Vrd, Vdd, Vss, Vout, Vguard.

- 3. Includes pins:  $\phi$ V1,  $\phi$ V2,  $\phi$ H1,  $\phi$ H2.

- 4. Includes pins:  $\phi R$ , Vog.

- 5. Voltage difference between overlapping gates. Includes:  $\phi$ V1 to  $\phi$ V2,  $\phi$ H1 to  $\phi$ H2,  $\phi$ V2 to  $\phi$ H1,  $\phi$ H2 to Vog.

- 6. Avoid shorting output pins to ground or any low impedance source during operation.

- 7. T=25°C. Excessive humidity will degrade MTTF.

CAUTION: This device contains limited protection against Electrostatic Discharge (ESD). Devices should be handled in accordance with strict ESD procedures for Class 0 devices (JESD22 Human Body Model) or Class A (Machine Model). Refer to Application Note MTD/PS-0224, "Electrostatic Discharge Control"

### **3.2 DC Operating Conditions**

| Description             | Symbol | Min. | Nom. | Max. | Units | Max DC Current | Notes |

|-------------------------|--------|------|------|------|-------|----------------|-------|

|                         |        |      |      |      |       | (mA)           |       |

| Reset Drain             | Vrd    | 10.5 | 11   | 11.5 | V     | 0.01           |       |

| Output Amplifier Return | Vss    | 1.5  | 2.0  | 2.5  | V     | 0.45           |       |

| Output Amplifier Supply | Vdd    | 14.5 | 15   | 15.5 | V     | Iout           |       |

| Substrate               | Vsub   | 0    | 0    | 0    | V     | 0.01           |       |

| Output Gate             | Vog    | 3.75 | 4.0  | 5.0  | V     | 0.01           |       |

| Guard Ring              | Vguard | 8.0  | 10.0 | 12.0 | V     | 0.01           |       |

| Video Output Current    | Iout   |      | -5   | -10  | mA    | -              | 1     |

#### Notes:

1. An output load sink must be applied to Vout to activate output amplifier - see Figure below.

### Figure 4 - Recommended Output Structure Load Diagram

Eastman Kodak Company - Image Sensor Solutions

#### 3.3 AC Operating Condition

| Description                    | Symbol      | Level | Min.  | Nom.  | Max. | Units | Effective<br>Capacitance | Notes |

|--------------------------------|-------------|-------|-------|-------|------|-------|--------------------------|-------|

| Vertical CCD Clock - Phase 1   | φV1         | Low   | -10.5 | -10.0 | -9.5 | V     | 82 nF                    |       |

|                                |             | High  | 0.5   | 1.0   | 1.5  | V     | (all \$V1 pins)          |       |

| Vertical CCD Clock - Phase 2   | φV2         | Low   | -10.5 | -10.0 | -9.5 | V     | 820 nF                   |       |

|                                |             | High  | 0.5   | 1.0   | 1.5  | V     | (all \\$V2 pins)         |       |

| Horizontal CCD Clock - Phase 1 | фН1         | Low   | -6.0  | -3.0  | -3.0 | V     | 400 pF                   |       |

|                                | -           | High  | 4.0   | 7.0   | 7.0  | V     |                          |       |

| Horizontal CCD Clock - Phase 2 | <b></b> ФН2 | Low   | -6.0  | -3.0  | -3.0 | V     | 400 pF                   |       |

|                                |             | High  | 4.0   | 7.0   | 7.0  | V     |                          |       |

| Reset Clock                    | φR          | Low   | -4.0  | -3.0  | -2.0 | V     | 10pF                     |       |

|                                |             | High  | 3.5   | 4.0   | 5.0  | V     |                          |       |

#### Notes:

- 1. All pins draw less than 10uA DC current.

- 2. Capacitance values relative to VSUB.

#### **3.4** AC Timing Conditions

| Description                | Symbol               | Min.  | Nom. | Max. | Units | Notes   |

|----------------------------|----------------------|-------|------|------|-------|---------|

| φH1, φH2 Clock Frequency   | f <sub>H</sub>       |       | 4    | 15   | MHz   | 1, 2, 3 |

| φV1, φV2 Clock Frequency   | $f_V$                |       | 25   | 50   | kHz   | 1, 2, 3 |

| Pixel Period (1 Count)     | te                   | 67    | 250  |      | ns    |         |

| φH1, φH2 Setup Time        | t <sub>¢HS</sub>     | 0.5   | 1    |      | us    |         |

| φV1, φV2 Clock Pulse Width | $t_{\phi V}$         | 10    | 20   |      | us    | 2       |

| Reset Clock Pulse Width    | t <sub>øR</sub>      | 10    | 20   |      | ns    | 4       |

| Readout Time               | t <sub>readout</sub> | 531   | 1719 |      | ms    | 5       |

| Integration Time           | t <sub>int</sub>     |       |      |      |       | 6       |

| Line Time                  | t <sub>line</sub>    | 258.2 | 836  |      | us    | 7       |

#### Notes:

- 1. 50% duty cycle values.

- 2. CTE may degrade above the nominal frequency.

- 3. Rise and fall times (10/90% levels) should be limited to 5-10% of clock period. Cross-over of register clocks should be between 40-60% of amplitude.

- 4.  $\phi R$  should be clocked continuously.

- 5.  $t_{readout} = (2056 * t_{line})$

- 6. Integration time is user specified. Longer integration times will degrade noise performance.

- 7.  $t_{\text{line}} = (3 * t_{\phi V}) + t_{\phi HS} + (3100 * t_{e}) + t_{e}$

Eastman Kodak Company - Image Sensor Solutions

# Performance Specification

# KAF-6303E

3089-3098 3099-3100

Dummy Pixels

16 - 3088

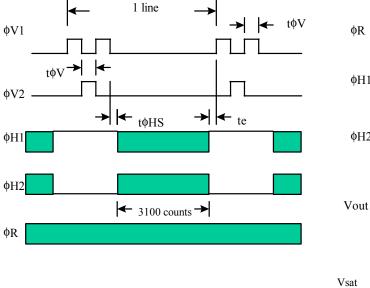

**Pixel Timing Detail**

VsatSaturated pixel video output signalVdarkVideo output signal in no light situation, not zero due to JdarkVpixPixel video output signal level, more electrons =more negativeVodcVideo level offset with respect to vsubVsubAnalog Ground

\* See Image Aquisition section (page 4)

**Line Content**

Photoactive Pixels

Dark Reference Pixels

1-10 11-16

Eastman Kodak Company - Image Sensor Solutions

#### 4.1 **Performance Specifications**

All values measured at 25°C, and nominal operating conditions. These parameters exclude defective pixels.

| Description                                                                                                                               | Symbol         | Min.                      | Nom.                       | Max.                       | Units                                         | Notes |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------|----------------------------|----------------------------|-----------------------------------------------|-------|

| Saturation Signal<br>Vertical CCD capacity<br>Horizontal CCD capacity<br>Output Node capacity                                             | Nsat           | 85000<br>170000<br>190000 | 100000<br>200000<br>220000 | 120000<br>240000<br>240000 | electrons / pixel                             | 1     |

| Red Quantum Efficiency ( $\lambda$ =650nm)<br>Green Quantum Efficiency ( $\lambda$ =550nm)<br>Blue Quantum Efficiency ( $\lambda$ =450nm) | Rr<br>Rg<br>Rb | 52<br>42<br>32            | 65<br>52<br>40             | 75<br>62<br>48             | %<br>%<br>%                                   |       |

| Photoresponse Non-Linearity                                                                                                               | PRNL           |                           | 1                          | 2                          | %                                             | 2     |

| Photoresponse Non-Uniformity                                                                                                              | PRNU           |                           | 1                          | 3                          | %                                             | 3     |

| Dark Signal                                                                                                                               | Jdark          |                           | 15<br>3.5                  | 50<br>10                   | electrons / pixel / sec<br>pA/cm <sup>2</sup> | 4     |

| Dark Signal Doubling Temperature                                                                                                          |                | 5                         | 6.3                        | 7.5                        | °C                                            |       |

| Dark Signal Non-Uniformity                                                                                                                | DSNU           |                           | 15                         | 50                         | electrons / pixel / sec                       | 5     |

| Dynamic Range                                                                                                                             | DR             | 70                        | 74                         |                            | dB                                            | 6     |

| Charge Transfer Efficiency                                                                                                                | CTE            | 0.99997                   | 0.99999                    |                            |                                               |       |

| Output Amplifier DC Offset                                                                                                                | Vodc           | 9.5                       | 10.5                       | 11.5                       | V                                             | 7     |

| Output Amplifier Bandwidth                                                                                                                | f-3dB          |                           | 45                         |                            | Mhz                                           | 8     |

| Output Amplifier Sensitivity                                                                                                              | Vout/Ne~       | 9                         | 10                         | 11                         | uV/e~                                         |       |

| Output Amplifier output Impedance                                                                                                         | Zout           | 175                       | 200                        | 250                        | Ohms                                          |       |

| Noise Floor                                                                                                                               | ne~            |                           | 15                         | 20                         | electrons                                     | 9     |

Notes:

- For pixel binning applications, electron capacity up to 330000 can be achieved with modified CCD inputs. Each sensor may have to be optimized individually for these applications. Some performance parameters may be compromised to achieve the largest signals.

- 2. Worst case deviation from straight line fit, between 1% and 90% of Vsat.

- 3. One Sigma deviation of a 128x128 sample when CCD illuminated uniformly.

- 4. Average of all pixels with no illumination at 25°C.

- 5. Average dark signal of any of 12 x 8 blocks within the sensor. (each block is 128 x 128 pixels)

- 6.  $20\log(Nsat / ne~)$  at nominal operating frequency and  $25^{\circ}C$ .

- 7. Video level offset with respect to ground

- 8. Last output amplifier stage only. Assumes 10pF off-chip load..

- 9. Output noise at  $25^{\circ}$ C, nominal operating frequency, and tint = 0.

Eastman Kodak Company - Image Sensor Solutions

Performance Specification

KAF-6303E

## 4.2 Typical Performance Characteristics

Eastman Kodak Company - Image Sensor Solutions

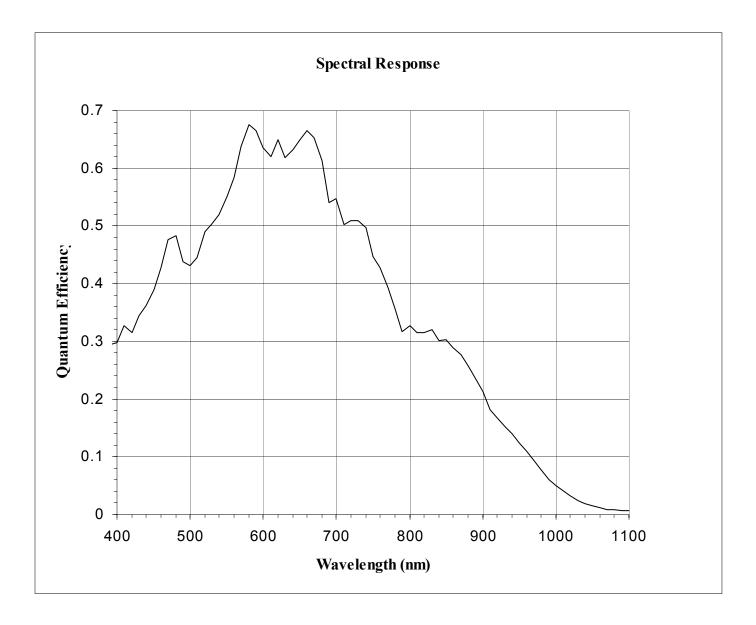

#### 4.3 Cosmetic Classification

Defect tests performed at T=25°C

| Class | Point | Defects | Cluster Defects |        | Maximum<br>Cluster Size | Column | Defects |

|-------|-------|---------|-----------------|--------|-------------------------|--------|---------|

|       | Total | Zone A  | Total           | Zone A |                         | Total  | Zone A  |

| C1    | ≤35   | ≤14     | ≤5              | ≤2     | 2                       | 0      | 0       |

| C2    | ≤90   | ≤45     | ≤36             | ≤18    | 5                       | 0      | 0       |

| Point Defect            | Dark: A pixel which deviates by more than 6% from<br>neighboring pixels when illuminated to 70% of saturation, OR<br>Bright: A Pixel with dark current > 10,000 e/pixel/sec at 25°C. |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cluster Defect          | A grouping of not more than "Maximum Cluster Size" defects                                                                                                                           |

| Column Defect           | A grouping of >5 contiguous point defects along a single column, OR                                                                                                                  |

|                         | A column containing a pixel with dark current >                                                                                                                                      |

|                         | 30,000e/pixel/sec, OR A column that does not meet the CTE                                                                                                                            |

|                         | specification for all exposures less than the specified Max sat.<br>signal level and greater than 2 Ke, OR                                                                           |

|                         | A pixel which loses more than 250 e under 2Ke illumination.                                                                                                                          |

| Neighboring pixels      | The surrounding 128 x 128 pixels or $\pm 64$ columns/rows.                                                                                                                           |

| Defect Separation       | Column and cluster defects are separated by no less than two (2) pixels in any direction (excluding single pixel defects).                                                           |

| Defect Region Exclusion | Defect region excludes the outer two (2) rows and columns at each side/end of the sensor.                                                                                            |

Eastman Kodak Company - Image Sensor Solutions

#### 5.1 Quality Assurance and Reliability

**Quality Strategy:** All image sensors will conform to the specifications stated in this document. This will be accomplished through a combination of statistical process control and inspection at key points of the production process. Typical specification limits are not guaranteed but provided as a design target. For further information refer to ISS Application Note MTD/PS-0292, Quality and Reliability.

**Replacement:** All devices are warranted against failure in accordance with the terms of Terms of Sale. This does not include failure due to mechanical and electrical causes defined as the liability of the customer below.

Liability of the Supplier: A reject is defined as an image sensor that does not meet all of the specifications in this document upon receipt by the customer.

**Liability of the Customer:** Damage from mechanical (scratches or breakage), electrostatic discharge (ESD) damage, or other electrical misuse of the device beyond the stated absolute maximum ratings, which occurred after receipt of the sensor by the customer, shall be the responsibility of the customer.

**Cleanliness:** Devices are shipped free of mobile contamination inside the package cavity. Immovable particles and scratches that are within the imager pixel area and the corresponding cover glass region directly above the pixel sites are also not allowed. The cover glass is highly susceptible to particles and other contamination. Touching the cover glass must be avoided. See ISS Application Note MTD/PS-0237, Cover Glass Cleaning for Image Sensors, for further information.

**ESD Precautions:** Devices are shipped in static-safe containers and should only be handled at static-safe workstations. See ISS Application Note MTD/PS-0224, Electrostatic Discharge Control, for handling recommendations.

**Reliability:** Information concerning the quality assurance and reliability testing procedures and results are available from the Image Sensor Solutions and can be supplied upon request. For further information refer to ISS Application Note MTD/PS-0292, Quality and Reliability.

**Test Data Retention:** Image sensors shall have an identifying number traceable to a test data file. Test data shall be kept for a period of 2 years after date of delivery.

**Mechanical:** The device assembly drawing is provided as a reference. The device will conform to the published package tolerances.

Eastman Kodak Company - Image Sensor Solutions

#### 5.2 Ordering Information

Address all inquiries and purchase orders to:

Image Sensor Solutions Eastman Kodak Company Rochester, New York 14650-2010 Phone: (585) 722-4385 Fax: (585) 477-4947 Web: <u>www.kodak.com/go/imagers</u> E-mail: ccd@kodak.com

Eastman Kodak reserves the right to change any information contained herein without notice. All information furnished by Eastman Kodak is believed to be accurate.

#### WARNING: LIFE SUPPORT APPLICATIONS POLICY

Kodak image sensors are not authorized for and should not be used within Life Support Systems without the specific written consent of the Eastman Kodak Company. Product warranty is limited to replacement of defective components and does not cover injury or property or other consequential damages.

Eastman Kodak Company - Image Sensor Solutions

## **Revision Changes**

| Revision<br>Number | Description of Changes                                                                         |

|--------------------|------------------------------------------------------------------------------------------------|

| 0                  | Original formal version.                                                                       |

| 1                  | Added UV Enhancement class (Section 4.3).                                                      |

|                    | Removed Appendix 1 Available Part Numbers.                                                     |

|                    | Added Revision Changes.                                                                        |

| 2                  | Revised Class 1 cosmetic specification. (Page 13)                                              |

|                    | Removed UV Enhanced device. (Page 13)                                                          |

|                    | Revised ESD classification to Class 0 HBM. This is not a change to the device, simply defining |

|                    | more accurately using updated classifications. (Page 7)                                        |

| 3.0                | Section 4.3 Cosmetic Specification:                                                            |

|                    | Remove Class 3, Revise Class 2 as follows:                                                     |

|                    | Point Defects: Total 90, Zone A 45                                                             |

|                    | Clusters: Total 36, Zone A 18                                                                  |

|                    | Columns Total 0                                                                                |

|                    | Section 5.1, Quality and Reliability, updated.                                                 |

| 3.1                | Section 3.3 AC Operating Conditions:                                                           |

|                    | Change Horizontal CCD Clock voltages for Phase 1 and Phase 2 as follow:                        |

|                    | Low Nominal from –4.0 to –3.0V                                                                 |

|                    | Low Max. from $-3.5$ to $-3.0$ V                                                               |

|                    | High Nominal from 6.0 to 7.0V                                                                  |

|                    | High Max. from 6.5 to 7.0V                                                                     |

|                    | Corrected V1, V2 Clock Capacitance from 820 to 82nF                                            |

|                    | Updated ESD Caution.                                                                           |

Eastman Kodak Company - Image Sensor Solutions